# INTERLOCK AND PROTECTION SCHEME OF 60 kW and 1 MW RF SYSTEMS FOR ACCELERATOR

Sonal Sharma, Sandip Shrotriya, Manjiri Pande, Shiju A, Niranjan Patel, and V.K.Handu Technical Physics Division, Bhabha Atomic Research Centre, Mumbai, India 400094

#### Abstract

A high power radio frequency (RF) system is always equipped with an interlock and protection circuit for its reliable and safe operation. In BARC, a 60 kW, 350 MHz RF system for 400 KeV deuterium RFQ and a one MW klystron based RF system for proton accelerator [1] is being developed. In an RF system, RF input, all the DC/AC bias supplies and water cooling parameters like flow, temperature need to be switched ON/OFF in a certain predefined timing sequence to prevent damage to the high power RF device and its system. This is ensured by a properly designed interlock circuit. Additionally, a protection circuit senses the fault conditions such as overvoltage, over-current, high water/air temperature, low water flow, arcing etc. and generates trips which in turn switch off the supplies in a controlled sequence. The present interlock circuit for 60 kW system is opamp/comparator based. For better reliability and stability, a PLC based system is being developed. Similarly, for klystron based RF system, a detailed design scheme has been designed based on its various operating modes. This paper describes in detail, the designed schemes for both tetrode and klystron based RF systems and for both analog and PLC based interlock and protection systems.

## INTERLOCK AND PROTECTION SCHEME FOR 60 kW RF SYSTEM

The 400 KeV deuterium radio frequency quadrupole (RFQ) accelerator requires about 70 kW of RF power. Hence, two 35 kW RF power amplifiers [2] are being developed to feed the RF power to this RFQ at two ports. Presently one such system has been installed and tested across 50-ohm resistive load. To energize the RF system in a safe and reliable mode, all the bias supplies, RF driver and cooling circuits need to be switched ON/OFF in a predefined time sequence to prevent damage to the high power RF devices. A suitable interlock and protection circuit has been designed and developed which takes care of this. The RF system has been tested upto 14 kW power.

## Architecture of Interlock and Protection

Architecture of the interlock and protection circuit has been built as per the guidelines laid out in the data sheet of main RF power device TH 571B [3], which specifies detail specifications. The necessary electrical signals are derived from each of the bias supplies.

## Analog based scheme

#### Interlock sequence

This scheme is opamp/comparator based. The scheme is such that the bias supplies for tetrode are switched on in following sequence:

- 1. Low conductive water cooling

- 2. Filament supply

- 3. Control grid supply

- 4. Anode supply

- 5. Screen supply

- 6. RF drive

Cooling is the most important aspect for protection of RF amplifier. Before switching on the amplifier, cooling conditions need to be ensured. Interlock circuit takes care of this. Only after verifying the cooling conditions, the circuit starts its operation. The sequence starts with checking of water flows for anode, screen and filament in the outlet and temperature of water. When the interlock circuit receives cooling verification signal, it compares this with the reference value and switches on the filament supply. The filament supply then slowly ramps the filament voltage in 15 minutes and then control grid voltage is switched on to a predefined set value. After stabilisation period of two minutes and confirmation of read back signal from both supplies, a signal switches on the anode supply. It has a provision of accepting a external or remote input ( in 4 to 20 mA format) to ramp up its output voltage to a preset value. The read back signal (10 V) from anode supply confirms that anode bias is established. Then, screen grid supply is switched on and the RF system is ready in DC bias mode.

#### Protection sequence

In parallel to interlocking, the protection circuit keeps a check on any fault such as low water flow, high water temperature, screen overvoltage /overload, anode overvoltage/overload, control grid under voltage / overload, etc. The protection circuit senses these trips and switches off the required bias supplies in a predefined sequence in response to the particular trip generated. For example, when screen overload is sensed, the protection circuit switches off RF drive and screen supply. Thus the tube is protected against any fault. The RF system has spark gap based crowbar protection and IGBT switch based protection. These signals are used in the protection scheme and have highest priority.

## PLC based scheme:

For better system reliability and stability, it has been thought of using programmable logic controller (PLC) based system. The PLC based system reduces the analog based circuitry and the hardwired complexities are decreased. It is designed for multi input and output arrangement and the output must be produced in response to input conditions within a bounded time. Based on the logic implemented in the program, PLC determines which actions need to be executed with output instruments

The hardware of interlock system is based on Siemens PLC [4]. The processor used is S7-200, CPU 224.The system can be controlled by touch screen at local mode or Ethernet network with high level Human-Machine Interface (HMI) interface. The touch screen can be easily handled by the user via RS232 communication with PC and PLC. The whole PLC system consists of various modules of digital input, digital output, analog input, analog output, power supply, input and output interfacing modules etc. The no of digital inputs are 14, digital outputs are 10 and analog inputs are 04. The PLC programming is done by using ladder logic and the software used is Simetic STEP-7 Micro/WIN 32.

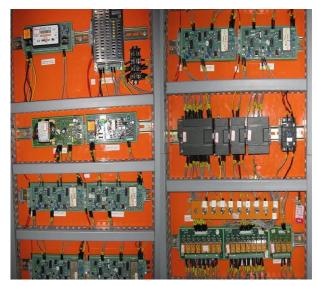

Fig. 1: Photograph of PLC panel

## INTERLOCK PROTECTION SCHEME FOR 1 MW KLYSTRON

Three klystron [5] based RF systems [6] of power 1 MW at 352.2 MHz are required for Low Energy High Intencity Proton Accelerator (LEHIPA). Each RF system requires a very reliable and fast acting interlock and protection circuit for its safe operation. To design this circuit, a detail investigation of specifications / data sheets of klystron, Y junction circulator [7], 1 MW RF load, RF transmission line and all the DC bias supplies was done. Klystron is very sensitive and prone to damage because of energy dissipated across it in case of any fault occurring during sparking / arcing across any part of RF system. So, special care is taken to avoid such stored energy across each bias supplies. Also fast acting protection has been incorporated which takes action based on signals arising from arc detectors mounted at various locations of the whole RF system. The interlock and protection scheme is PLC based.

## **Operating Sequence and Modes**

## Interlock sequence

A detail sequence control scheme including all the fault parameters was evolved. The entire operation sequence of the klystron based RF system has been divided into five modes such as start mode, heater mode, standby mode, high voltage mode and RF mode. The sequence starts with the start mode by monitoring the vacuum conditions, predefined safety parameters like door interlocks, X-ray shielded cage interlocks etc. and water cooling parameters. After satisfying the predefined conditions, it proceeds to heater mode and starts with ramping up of filament voltage in around 15 minutes and then electromagnet supplies are switched ON. The next mode is standby mode where all status parameters like vacuum, filament current, electromagnet current, cooling water flows and water temperature of RF system are reviewed. Then HV mode starts with switching on of cathode bias in a smooth ramping mode and then similarly anode bias is established. Throughout this entire sequence, vacuum parameters and water flow parameters are continuously monitored. Final mode is RF mode where low level RF drive is switched on.

#### Protection sequence

In addition to interlocking sequence, the PLC scheme takes care of the protections like faults or trips generated because of low water flows, high outlet water temperature, over voltage and over current, under voltage in all the bias supplies, arc detection from klystron window, circulator, RF windows and vacuum deterioration etc. As soon as any fault is detected, a pre dermined action will be taken by PLC.

## ACKNOWLEDGEMENT

Authors wish to thank Dr.S.Kailas, Director, Physics group for his constant encouragement and support.

#### REFERENCES

S.S Kapoor, BARC internal report 'Road map for development of accelerator driven sub-critical reactor systems'

[2] Manjiri Pande et al," Development of 35 kW power amplifier at 350 MHz for RFQ based neutron generator" APAC 2007, Indoor, WEPMA 145,

- [3] Data sheet of TH 571B

- [4] Siemens manual from PLC

- [5] Data sheet of Thales klystron TH 2089F

- [6] Manjiri Pande et al, 'High power RF system for 3MeV RFQ accelerator' DAE symposium on nuclear physics, December11-15, 2007, Sambalpur University, Orisa

- [7] Data sheet of AFT circulator